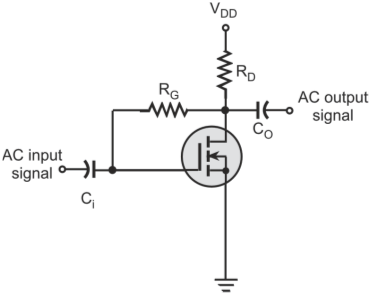

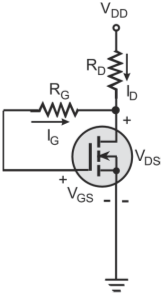

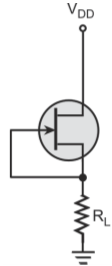

Similar to the common-collector configuration, the common-drain configuration also offers high input impedance, low output impedance, nearly unity voltage gain and no input–output phase reversal.

Discover, Learn and Innovate

Your Trusted Online Resource for Electronics

Share on Social Media

Popular Post

Popular Post

© 2023 Electronicspedia All Rights Reserved | Designed by Aarohan Research Lab